Ultra High-Speed Mixed Signal ASICs

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

## ASNT6902-MOD

## 56Gbaud PAM4 Data Generator with USB Control

- Adjustable data output amplitude and eye quality

- Output data eye cross point adjustment

- Internal precision low jitter (below 1ps p-p) frequency synthesizer

- Alternate external reference clock input

- Differential CML PAM4 data output interface

- Can be used as a PRBS Data Generator up to 56*Gbaud*

- Reference clock-divided-by-2 outputs for four external PRBS generators

- Precision delay adjustment on clock input

- USB port for connection to an external PC

- Full functional control from GUI software

- Single +12*V* power supply from an external AC-DC converter

- High speed 1.85mm connectors for PAM4 differential data output

- Low jitter and limited temperature variation over industrial temperature range

Fig. 1. Front and back views of the unit

### DESCRIPTION

The ADSANTEC's differential PAM4 generator unit can be used for test applications, design verification, and R&D environments. The fully self-sustained device is integrated in a box with power conditioning, control circuitry, and a USB computer interface. All signal I/O's are CML-type. The front panel of the instrument is shown in Fig. 1 (top). It includes connectors as described in Table 1.

| Connector               |                | DESCRIPTION                                                     |  |  |  |

|-------------------------|----------------|-----------------------------------------------------------------|--|--|--|

| Name                    | Type           |                                                                 |  |  |  |

| High-Speed I/Os         |                |                                                                 |  |  |  |

| PAM4 DATA OUT P         | 1.85 <i>mm</i> | DC-coupled CML differential data output port, requires external |  |  |  |

| PAM4 DATA OUT N         | female         | SE 500hm terminations to ground                                 |  |  |  |

| CLOCK IN                | 2.92 <i>mm</i> | AC-coupled CML SE clock input port with internal SE 500hm       |  |  |  |

|                         | female         | terminations to ground                                          |  |  |  |

| DATA IN P11             |                |                                                                 |  |  |  |

| DATA IN N11             |                |                                                                 |  |  |  |

| DATA IN P12             |                |                                                                 |  |  |  |

| DATA IN N12             | 2.92 <i>mm</i> | DC-coupled CML differential data input ports, requires external |  |  |  |

| DATA IN P21             | female         | SE 500hm terminations to ground                                 |  |  |  |

| DATA IN N21             |                |                                                                 |  |  |  |

| DATA IN P22             |                |                                                                 |  |  |  |

| DATA IN N22             |                |                                                                 |  |  |  |

| CLOCK 1/2 OUT1 Q11, Q12 | SMA            | AC-coupled CML SE clock output ports, require external SE       |  |  |  |

| CLOCK 1/2 OUT2 Q21, Q22 | SMA            | 50 <i>Ohm</i> terminations to ground                            |  |  |  |

The back panel of the instrument is shown in Fig. 1 (bottom). It contains a power switch (Power), a power supply female connector (+9-12V DC) for connecting a male 2.5x5.5-barrel jack from an external AC-DC adapter (included), and a USB-A connector (USB) for connecting an external PC with installed Windows GUI control software (USB cable included).

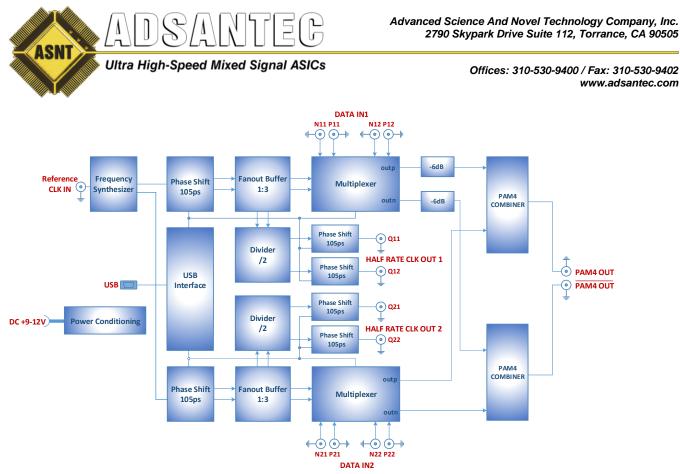

Fig.2 Block diagram of the 56Gbaud PAM4 Data Generator with USB control

The system consists of four main parts: Frequency Synthesizer, two high-speed 2:1 Multiplexers, two high-speed differential PAM4 combiners, and a Power Supply unit.

The Frequency Synthesizer generates internal clock signals that are used by other parts of the system.

The two incoming pairs of PRBS signals are processed by two 2:1 MUXes to produce two PRBS signals with doubled data rate. The MUXes also provide the clocks required for the Four-Channel external PRBS Generator. The clock phases may be individually adjusted in each MUX2:1 module via the system's USB control interface.

The output signals from 2:1 MUXes are mixed in two PAM4 combiners to form a differential PAM4 signal. The output amplitude of this signal may be adjusted. The amplitude of the middle eye opening can be individually adjusted without affecting the top and bottom eye opening amplitudes. Alternatively, the system may be programmed to output high-speed PRBS data instead of PAM4 data through the same I/Os (Fig. 3a).

All the parameters of this PAM4 Generator are controlled by an external PC through a USB port. A special GUI software is installed on the PC to simplify the system control.

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

# ELECTRICAL CHARACTERISTICS

| PARAMETER              | TYPICAL | UNIT  | COMMENT                             |  |  |  |  |

|------------------------|---------|-------|-------------------------------------|--|--|--|--|

| General Parameters     |         |       |                                     |  |  |  |  |

| Vcch                   | 9-12    | V     | Power Supply                        |  |  |  |  |

| Vccm                   | 5       | V     | Internal Power Supply               |  |  |  |  |

| Vccl                   | 3.3     | V     | Internal Power Supply               |  |  |  |  |

| Vee                    | 0       | V     | External Ground                     |  |  |  |  |

| Power Consumption      | 22.5    | W     |                                     |  |  |  |  |

| Input Reference Clock  |         |       |                                     |  |  |  |  |

| Frequency              | 1.5-2   | GHz   | From External Frequency Synthesizer |  |  |  |  |

| Jitter                 | 1       | ps    |                                     |  |  |  |  |

| Output Data            |         |       |                                     |  |  |  |  |

| Data Rate              | 1-56    | Gbaud |                                     |  |  |  |  |

| Maximum Output         | 1.2     | V     | Differential pk-pk                  |  |  |  |  |

| Amplitude              |         |       |                                     |  |  |  |  |

| Rise / Fall Time       | 8       | ps    | 80%-20%                             |  |  |  |  |

| TDECQ (no FFE)         | 1.5     | dB    | With Rx Optimizer                   |  |  |  |  |

| TDECQ (with 5-tap FFE) | 1.2     | dB    | With Rx Optimizer                   |  |  |  |  |

| Output Clock           |         |       |                                     |  |  |  |  |

| Frequency              | 12-16   | GHz   | Internal Clock divided by 2         |  |  |  |  |

Table 2. PAM4 Generator Specifications

Ultra High-Speed Mixed Signal ASICs

ASNI

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

(b)

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

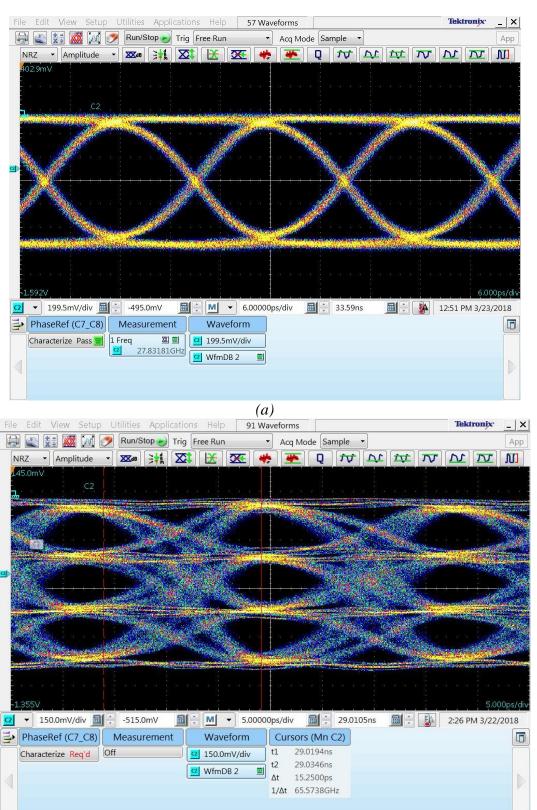

Fig.3 a). Measured 56 Gb/s NRZ EYE diagram of the ASNT PAM4 Generator unit with Tektronix Analyzer; b) Measured 56 Gbaud/s PAM4 EYE diagram of the ASNT PAM4 Generator unit with Tektronix Analyzer

### **MECHANICAL DIMENSIONS**

| PARAMETER | ТҮР | UNIT | COMMENTS |

|-----------|-----|------|----------|

| Length    | TBD | mm   |          |

| Width     | TBD | mm   |          |

| Height    | TBD | mm   |          |

|           |     |      |          |

#### **REVISION HISTORY**

| Revision | Date    | Changes                                  |  |  |

|----------|---------|------------------------------------------|--|--|

| 1.0.2    | 07-2019 | Updated Letterhead                       |  |  |

| 1.0.1    | 05-2018 | Corrected title<br>Corrected description |  |  |

|          |         | Added Table with connector descriptions  |  |  |

| 0.0.1    | 01-2018 | Initial Release                          |  |  |