27 Via Porto Grande, Rancho Palos Verdes, CA, 90275.

Ph. # 1-310-377-6029.

Fax # 1-310-377-9940.

# ASNT5079-PQC 14GHz Clock, 17Gbps Data Phase Shifter with Linear OB

- Broadband (10MHz-14GHz/20Mbps-17Gbps) tunable clock/data phase shifter with 250ps of delay variation.

- Exhibits low jitter and limited temperature variation over industrial temperature range.

- 1GHz of bandwidth for the phase adjustment tuning port.

- Fully differential input and output buffers with on-chip  $50\Omega$  termination.

- Linearized data output for minimized undershoot/overshoot.

- CML output interface with 600mV single-ended swing.

- Single  $\pm 3.3V$  power supply.

- Power consumption: 1.6*W*.

- Fabricated in SiGe for high performance, yield, and reliability.

- Standard MLF/QFN 24-pin package.

Rev.: 4, January 2009.

ASNT5079-PQC

27 Via Porto Grande, Rancho Palos Verdes, CA, 90275.

Ph. # 1-310-377-6029.

Fax # 1-310-377-9940.

### **DESCRIPTION**

The temperature stable ASNT5079-PQC SiGe IC provides extremely low jitter broadband signal phase shifting capability between its input and output signal ports and is intended for use in high-speed measurement / test equipment. ASNT5079-PQC can process an up to 14GHz/17Gbps RF clock/data signal and deliver 0-250ps of adjustable phase delay through the up to 1GHz external adjustment of its differential tuning port. The part's I/Os support the CML logic interface with on chip  $50\Omega$  termination and may be used differentially, AC/DC coupled, single-ended, or in any combination. The output buffer is linearized for reduction of undershoot and overshoot. The part operates from a single  $\pm 3.3V$  power supply.

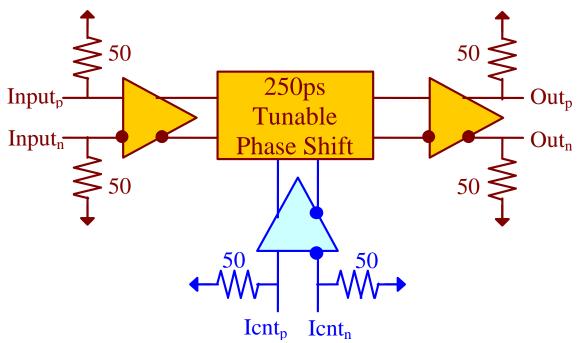

### FUNCTIONAL BLOCK DIAGRAM

#### TERMINAL FUNCTIONS

| TERMINAL   |                | TYPE   | DESCRIPTION                                           |  |  |

|------------|----------------|--------|-------------------------------------------------------|--|--|

| NAME (NO.) |                |        |                                                       |  |  |

| VCC        | 1,3,5,7,9,11   | PS     | Power Supply: 3.3V / 0V                               |  |  |

|            | 13-17,19,21,23 |        |                                                       |  |  |

| vee        | 6,12,18,24     | PS     | Power Supply: 0V / -3.3V                              |  |  |

| inp        | 20             | Input  | Differential CML high-speed signal inputs             |  |  |

| inn        | 22             |        |                                                       |  |  |

| outp       | 10             | Output | Differential CML high-speed signal outputs            |  |  |

| outn       | 8              |        |                                                       |  |  |

| icntp      | 2              | Input  | Differential low-speed phase adjustment tuning inputs |  |  |

| icntn      | 4              |        |                                                       |  |  |

Rev.: 4, January 2009.

ASNT5079-PQC

27 Via Porto Grande, Rancho Palos Verdes, CA, 90275.

Ph. # 1-310-377-6029.

Fax # 1-310-377-9940.

# **ELECTRICAL CHARACTERISTICS**

| PARAMETER                 | MIN      | TYP        | MAX      | UNIT     | COMMENTS         |

|---------------------------|----------|------------|----------|----------|------------------|

| VEE                       | -3.1     | 0.0 / -3.3 | 3 -3.5   | V        | ±6%              |

| VCC                       | 3.1      | 3.3 / 0.0  | 3.5      | V        | ±6%              |

| IEE                       | 450      | 475        | 500      | mA       |                  |

| Power                     |          | 1.6        |          | W        |                  |

| Junction Temp.            | -25      | 50         | 125      | °C       |                  |

| Input (in)                |          |            |          |          |                  |

| Data rate/Clock frequency | 0.0      |            | 17/14    | Gbps/GHz |                  |

| CM Level                  | Vcc-0.8  | 3 Vcc-0.   | .2 Vcc   | V        |                  |

| SE Swing                  | 50       | 400        | 1000     | mV       | Peak-to-Peak     |

| Output (out)              |          |            |          |          |                  |

| Data rate/Clock frequency | 0.0      |            | 17/14    | Gbps/GHz |                  |

| CM Level                  | Vcc-0.35 | Vcc-0.3    | Vcc-0.25 | V        |                  |

| SE Swing                  | 570      | 600        | 630      | mV       | Peak-to-Peak     |

| Rise/Fall Times           | 15       | 17         | 19       | ps       | 20%-80%          |

| Additive Jitter           |          | TBD        |          | ps       | Peak-to-Peak     |

| Duty Cycle                | 45%      | 50%        | 55%      |          | For clock signal |

| <b>Tuning Port (icnt)</b> |          |            |          |          |                  |

| Diff. Swing               | -500     |            | 500      | mV       | Peak-to-Peak     |

| CM Level                  | Vcc-0.5  | Vcc-0.2    | 25 Vcc   | V        |                  |

| Phase Shift               | 0        |            | 250      | ps       | $<\pm5\%$        |

| Shift Stability           | -24      |            | 24       | ps       | 0-125°C          |

| Bandwidth                 | 0.0      |            | 1000     | MHz      |                  |

# **PACKAGE INFORMATION**

The chip is packaged in a standard 24-pin QFN package. The package's mechanical information is available on the company's  $\underline{\text{website}}$ .

Rev.: 4, January 2009.

ASNT5079-PQC