# ASNT2031-MBL Digital DMUX 24-to-48 with SSTL Interface

- Digital demultiplexer (DMUX) 24-to-48 with SSTL1.5 input and output interfaces.

- Supports data rates from 1.0*Mbps* to 2.0*Gbps*.

- User-controllable independent internal delays for data and clock signals.

- 1.5V I<sup>2</sup>C control interface with a user-defined 3-bit chip address.

- Preset function for synchronization of multiple parallel devices.

- Full-rate output copy of external high-speed clock input signal.

- Two pairs of clock divided-by-2 and synchronous clock enable outputs for supporting the treetype demultiplexation structure.

- Additional synchronous clock divided-by-4 output.

- Dual power supply of +3.0V and +1.5V.

- Industrial temperature range.

- Low power consumption of 2.1W at 2.0Gbps.

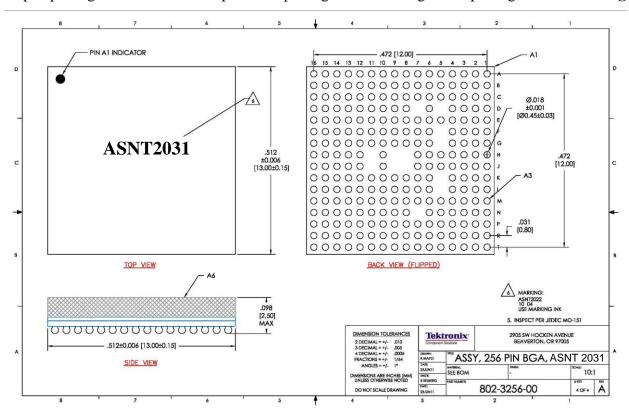

- Available in custom 256-pin BGA package (13mm x 13mm x 2.5mm).

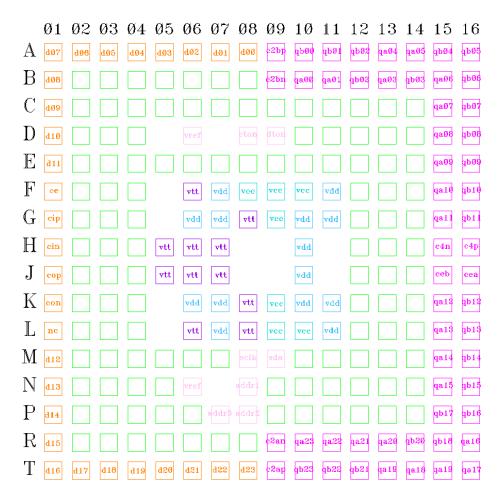

Fig. 1. BGA Ball Placement, view from the Top of Package.

#### DESCRIPTION

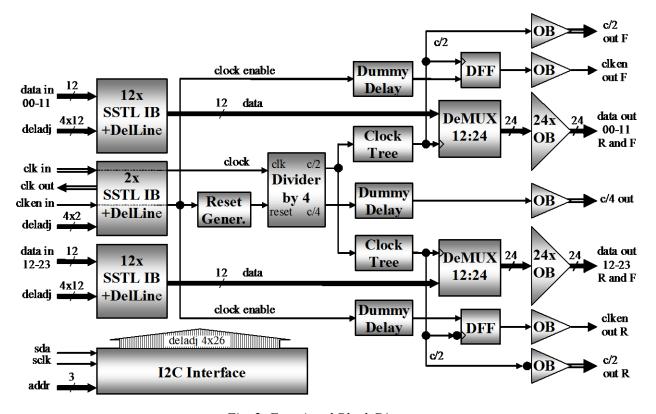

Fig. 2. Functional Block Diagram.

ASNT2031-MBL is a broad-band multi-channel digital deserializer-demultiplexer (DMUX) 24-to-48 with external initial preset functionality and 1.5V single-ended SSTL1.5 input and output interfaces for data and preset signals, as well as matching differential interfaces for clock signals.

The part includes active variable delay lines (DelLine) in each input data and clock path for accurate signal alignment at the DMUX register inputs in order to define the optimal sampling point for the input data signals (data in). The value of each delay is externally controlled through an I<sup>2</sup>C interface with a user-selectable 3-bit chip address.

The operational speed of DMUX is defined by an external clock signal (clk in) that is converted into the required timing signals by an internal divider and is also supplied to the output of the chip (clk out). The divider can be preset to a certain initial state by the external clock enable signal (clken in), which allows synchronization of multiple DMUX devices operating in parallel.

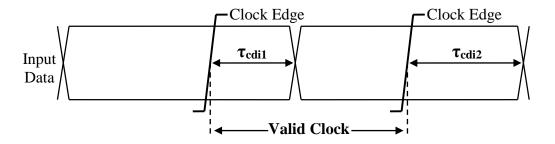

The optimal alignment of input data (data in) and clock is illustrated in Fig. 3. The actual values of setup ( $t_{SU}$ ) and hold ( $t_H$ ) times are presented in Table 6.

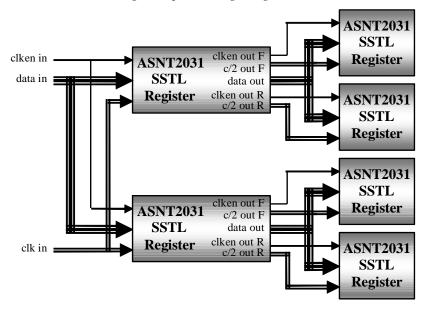

This part also supports cascaded tree-type structures as shown in Fig. 4, by supplying two synchronous copies of clock divided-by-2 (c/2 F, c/2 R) and clock enable (clken F, clken R) signals.

Clock divided-by-4 (c/4 out) output signal is also provided for higher flexibility.

Fig. 3. Input Timing Diagram.

Fig. 4. Cascaded Tree-Type Structure.

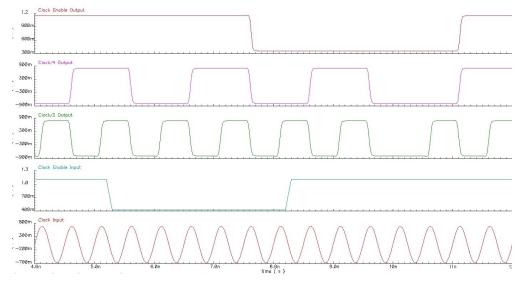

All clock and clock enable outputs are phase-aligned as shown in Fig. 5. The defined phase relations are stabilized over PVT variations.

Fig. 5. Clock Signals.

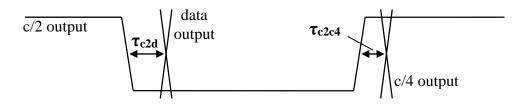

The output data alignment to the output clock divided-by-2 is illustrated in Fig. 6. It is also stabilized over PVT variations. The actual values of setup ( $t_{SU}$ ) and hold ( $t_H$ ) times are presented in Table 6.

Fig. 6. Output Data Alignment.

The DMUX IC uses two power supplies: vdd = +1.5V for CMOS I/Os and vcc = +3.0V for the internal circuitry. It consumes about 2.1W of power and is characterized for operation from  $-25^{\circ}C$  to  $125^{\circ}C$  of junction temperature.

# **SSTL Input Buffers**

The SSTL input buffer is designed as a differential current switch with high tolerance to input common-mode voltage level variation. In a differential mode used for clock inputs, it accepts two complementary signals and provides a selectable internal termination for both of them depending on the state of an internal switch. The switch is controlled by external 3.0V CMOS signal term\_on as shown in Table 1. A special external voltage vtt=vdd/2 should be provided for the correct operation of the termination circuit.

Table 1. Input Termination States.

| term_on signal state | Switch state | Termination type |

|----------------------|--------------|------------------|

| High                 | Closed       | 500hm to vtt     |

| Low                  | Open         | High impedance   |

The buffer can also operate in a single-ended mode used for data and clock enable inputs. In this mode, it accepts one input signal and external reference voltage vref=vdd/2. Deviations of the reference voltage may result in the duty cycle distortion of input signals.

## **Delay Lines**

Digitally-controlled on-chip active delay lines are used for the alignment of input clock and data signals in order to achieve the optimal sampling conditions at the inputs of the demultiplexer's internal register. Each delay line has 15 states with an absolute delay from 400ps to 1400ps. The accuracy of the minimum delay value is within  $\pm 20\%$  for the full PVT range. This relatively high variation is insignificant for the chip operation due to the matching delays in all input paths. The additional controllable delay of 1ns is highly stabilized and falls within  $\pm 5\%$  accuracy range.

The states of the delay lines are controlled within the 1-2-4-8 algorithm by signals provided from the internal I<sup>2</sup>C interface.

## **DeMUX 24:48**

The block consists of 24 independent demultiplexers 1-to-2 with the standard M-S/M-S-S architecture. It latches in the data signals on both edges of half-rate clock c/2 that is supplied by the internal divider-by-4

and delivers the descrialized outputs aligned to the corresponding clock edges. The output data signals are marked A and B and are aligned to the rising edge of c/2.

## Divider-by-4

The Divider-by-4 converts the input clock signal (clk in) into clock divided-by-2 (c/2) and clock divided-by-4 (c/4) signals aligned to a positive edge of the input clock. The divider can be preset to the 0 initial state by the external clken\_in signal that is preliminarily retimed by the input clock.

## **SSTL Output Buffers**

The SSTL output buffers are designed in full compliance with the SSTL1.5 standard and operate from a nominal 1.5V supply. Their CMOS driver can source or sink the required current through a 25*Ohm* series resistor. The output of the buffer may be 50*Ohm* terminated to an external voltage equal to a half of the buffer's supply voltage, or left non-terminated.

#### **Clock Enable and Divider Reset**

The clock enable signal must be at least 2 high-speed input clock periods long. The clock enable signal must be aligned with the falling edge of the high-speed input clock.

#### I<sup>2</sup>C Interface

This 2-wire 3.0V serial-to-parallel interface with initial preset (with the all "0" address word for reset) is used for setting the values of internal delays in the data and clock paths. The chip incorporates a Slave I<sup>2</sup>C device that supports write operations as described below.

The I<sup>2</sup>C system uses a serial data line (SDA) and a serial clock line (SCL) for data transfers. Data is transferred between Master and Slave synchronously on a byte-by-byte basis. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledgement bit set by Slave follows each transferred byte. Each bit is sampled during the high period of SCL.

The first byte of data transferred by Master immediately after START signal is the requested slave address. It consists of Vendor/Device code (currently 0xD) followed by Chip Address Addr[2:0] and an RW bit. The address of DMUX chip is defined by hard-wiring of 3 corresponding pins to either vee or vcc. The RW bit defines the type of operation: writing information from Master to Slave, or reading information by Master from Slave.

When RW=0 (write operation) and the requested address matches the preset slave address, the chip's I<sup>2</sup>C block responds by pulling the following bit (9-th acknowledgement bit) low. It then saves 4 LSBs of the next byte in the Input Address Register and returns another acknowledgement bit at the end of the second byte. After that, the block saves the next byte in the Input Data Register and returns acknowledgement bit one more time. During the same time, the interface transfers the previously stored byte of data from the Input Data Register to the internal register in accordance with the 4-bit address previously saved in the Input Address Register. The address assignment is detailed in Table 2.

Table 2. Internal Address Assignments.

| Address | Destination                                  | Data                    |

|---------|----------------------------------------------|-------------------------|

| 1'b0000 | Not Used                                     |                         |

| 1'b0001 | Delay for Data Channel 13 and 1              | Data[7:4] and Data[3:0] |

| 1'b0010 | Delay for Data Channel 14 and 2              | Data[7:4] and Data[3:0] |

| 1'b0011 | Delay for Data Channel 15 and 3              | Data[7:4] and Data[3:0] |

| 1'b0100 | Delay for Data Channel 16 and 4              | Data[7:4] and Data[3:0] |

| 1'b0101 | Delay for Data Channel 17 and 5              | Data[7:4] and Data[3:0] |

| 1'b0110 | Delay for Data Channel 18 and 6              | Data[7:4] and Data[3:0] |

| 1'b0111 | Delay for Data Channel 19 and 7              | Data[7:4] and Data[3:0] |

| 1'b1000 | Delay for Data Channel 20 and 8              | Data[7:4] and Data[3:0] |

| 1'b1001 | Delay for Data Channel 21 and 9              | Data[7:4] and Data[3:0] |

| 1'b1010 | Delay for Data Channel 22 and 10             | Data[7:4] and Data[3:0] |

| 1'b1011 | Delay for Data Channel 23 and 11             | Data[7:4] and Data[3:0] |

| 1'b1100 | Delay for Data Channel 24 and 12             | Data[7:4] and Data[3:0] |

| 1'b1101 | Delay for Clock Enable and Clock             | Data[7:4] and Data[3:0] |

| 1'b1110 | Not Used                                     |                         |

| 1'b1111 | Delay for Data Channels 13-to-24 and 1-to-12 | Data[7:4] and Data[3:0] |

#### **ABSOLUTE MAXIMUM RATINGS**

Caution: Exceeding the absolute maximum ratings shown in Table 3 may cause damage to this product and/or lead to reduced reliability. Functional performance is specified over the recommended operating conditions for power supply and temperature only. AC and DC device characteristics at or beyond the absolute maximum ratings are not assumed or implied. All min and max voltage limits are referenced to ground.

Table 3. Absolute Maximum Ratings.

| Parameter                   | Min | Max  | Units |

|-----------------------------|-----|------|-------|

| First Supply Voltage (vcc)  |     | +3.6 | V     |

| Second Supply Voltage (vdd) |     | +1.8 | V     |

| Power Consumption           |     | 2.3  | W     |

| RF Input Voltage Swing (SE) |     | 1.8  | V     |

| Case Temperature            |     | +90  | °C    |

| Storage Temperature         | -40 | +100 | °C    |

| Operational Humidity        | 10  | 98   | %     |

| Storage Humidity            | 10  | 98   | %     |

# **TERMINAL FUNCTIONS**

The ball assignment for the BGA package is shown in Table 4 and Table 5.

Table 4. Package Signal Balls.

| Name        | Code | Type                     | Description                      |

|-------------|------|--------------------------|----------------------------------|

|             |      | High-Speed I             | nputs                            |

| data in 00  | A8   | 1.5V CMOS input          | Single-ended data inputs         |

| data in 01  | A7   |                          |                                  |

| data in 02  | A6   |                          |                                  |

| data in 03  | A5   |                          |                                  |

| data in 04  | A4   |                          |                                  |

| data in 05  | A3   |                          |                                  |

| data in 06  | A2   |                          |                                  |

| data in 07  | A1   |                          |                                  |

| data in 08  | B1   |                          |                                  |

| data in 09  | C1   |                          |                                  |

| data in 10  | D1   |                          |                                  |

| data in 11  | E1   |                          |                                  |

| data in 12  | M1   |                          |                                  |

| data in 13  | N1   |                          |                                  |

| data in 14  | P1   |                          |                                  |

| data in 15  | R1   |                          |                                  |

| data in 16  | T1   |                          |                                  |

| data in 17  | T2   |                          |                                  |

| data in 18  | Т3   |                          |                                  |

| data in 19  | T4   |                          |                                  |

| data in 20  | T5   |                          |                                  |

| data in 21  | T6   |                          |                                  |

| data in 22  | T7   |                          |                                  |

| data in 23  | T8   |                          |                                  |

| clk in p    | G1   |                          | Differential clock inputs        |

| clk in n    | H1   |                          | _                                |

| clken in    | F1   |                          | Single-ended clock enable input  |

|             |      | High-Speed O             | utputs                           |

| clk out p   | J1   | SSTL 1.5 <i>V</i> output | Differential clock outputs       |

| clk out n   | K1   | •                        | -                                |

| c/2 out A p | T9   |                          | Differential clock outputs       |

| c/2 out A n | R9   |                          | -                                |

| c/2 out B p | A9   |                          | Differential clock outputs       |

| c/2 out B n | B9   |                          | -                                |

| c/4 out p   | H16  |                          | Differential clock outputs       |

| c/4 out n   | H15  |                          |                                  |

| clken out A | J16  |                          | Single-ended clock enable output |

| clken out B | J15  |                          | Single-ended clock enable output |

| Name          | Code | Туре             | Description               |

|---------------|------|------------------|---------------------------|

| data out A 00 | B10  | SSTL 1.5V output | Single-ended data outputs |

| data out B 00 | A10  | _                | _                         |

| data out A 01 | B11  |                  |                           |

| data out B 01 | A11  |                  |                           |

| data out A 02 | B12  |                  |                           |

| data out B 02 | A12  |                  |                           |

| data out A 03 | B13  |                  |                           |

| data out B 03 | B14  |                  |                           |

| data out A 04 | A13  |                  |                           |

| data out B 04 | A15  |                  |                           |

| data out A 05 | A14  |                  |                           |

| data out B 05 | A16  |                  |                           |

| data out A 06 | B15  |                  |                           |

| data out B 06 | B16  |                  |                           |

| data out A 07 | C15  |                  |                           |

| data out B 07 | C16  |                  |                           |

| data out A 08 | D15  |                  |                           |

| data out B 08 | D16  |                  |                           |

| data out A 09 | E15  |                  |                           |

| data out B 09 | E16  |                  |                           |

| data out A 10 | F15  |                  |                           |

| data out B 10 | F16  |                  |                           |

| data out A 11 | G15  |                  |                           |

| data out B 11 | G16  |                  |                           |

| data out A 12 | K15  |                  |                           |

| data out B 12 | K16  |                  |                           |

| data out A 13 | L15  |                  |                           |

| data out B 13 | L16  |                  |                           |

| data out A 14 | M15  |                  |                           |

| data out B 14 | M16  |                  |                           |

| data out A 15 | N15  |                  |                           |

| data out B 15 | N16  |                  |                           |

| data out A 16 | R16  |                  |                           |

| data out B 16 | P16  |                  |                           |

| data out A 17 | T16  |                  |                           |

| data out B 17 | P15  |                  |                           |

| data out A 18 | T14  |                  |                           |

| data out B 18 | R15  |                  |                           |

| data out A 19 | T13  |                  |                           |

| data out B 19 | T15  |                  |                           |

| data out A 20 | R13  |                  |                           |

| data out B 20 | R14  |                  |                           |

| Name          | Code | Type                     | Description                        |

|---------------|------|--------------------------|------------------------------------|

| data out A 21 | R12  | SSTL 1.5 <i>V</i> output | Single-ended data outputs          |

| data out B 21 | T12  |                          |                                    |

| data out A 22 | R11  |                          |                                    |

| data out B 22 | T11  |                          |                                    |

| data out A 23 | R10  |                          |                                    |

| data out B 23 | T10  |                          |                                    |

|               |      |                          |                                    |

| sda           | M9   | 1.5V CMOS input          | I2C bi-directional data signal     |

| sclk          | M8   |                          | I2C clock signal                   |

| add1          | N8   | 1.5V DC CMOS             | Chip address setup pins            |

| add2          | P8   | inputs                   |                                    |

| add3          | P7   |                          |                                    |

|               |      |                          |                                    |

| dton          | D9   | 3V DC CMOS               | Activation of internal termination |

| cton          | D8   | inputs                   | for data and clock inputs: "high"- |

|               |      |                          | termination "ON", "low"-           |

|               |      |                          | termination "OFF"                  |

Table 5. Package Power Supply Balls.

| Name | Code                            | Type                   | Value, V  |

|------|---------------------------------|------------------------|-----------|

| vee  | B2-B8, C2-C14, D2-D4, D10-D14,  | Ground                 | 0         |

|      | E2-E14, F2-F4, F12-F14, G2-G4,  |                        |           |

|      | G12-G14, H2-H4, H12-H14,        |                        |           |

|      | J2-J4, J12-J14, K2-K4, K12-K14, |                        |           |

|      | L2-L4, L12-L14, M2-M7,          |                        |           |

|      | M10-M14, N2-N5, N9-N14,         |                        |           |

|      | P2-P6, P9-P14, R2-R8            |                        |           |

| vcc  | F8, F9, F10, G9, K9, L9, L10    | Analog positive        | 2.9 - 3.3 |

|      |                                 | supply voltage         |           |

| vdd  | F7, F11, G6, G7, G10, G11, H10, | Digital positive       | 1.4 - 1.6 |

|      | J10, K6, K7, K10, K11, L7, L11  | supply voltage         |           |

| vtt  | F6, G8, H5, H6, H7,             | SSTL input             | vdd/2     |

|      | J5, J6, J7, K8, L6, L8          | termination voltage    |           |

| vref | D6, N6                          | Reference voltage      | vdd/2     |

|      |                                 | for SSTL input buffers |           |

| n/c  | L1                              | Not connected          |           |

| X    | D5, D7, F5, G5, H8, H9, H11,    | Removed balls          |           |

|      | J8, J9, J11, K5, L5, N7         |                        |           |

# **ELECTRICAL CHARACTERISTICS**

Table 6. Electrical Characteristics.

| PARAMETER                     | MIN   | TYP       | MAX         | UNIT        | COMMENTS          |

|-------------------------------|-------|-----------|-------------|-------------|-------------------|

| General Parameters            |       |           |             |             |                   |

| V <sub>CC</sub>               | +3.14 | +3.3      | +3.47       | V           | ±5%               |

| $V_{DD}$                      | +1.43 | +1.5      | +1.57       |             |                   |

| V <sub>EE</sub>               |       | 0.0       |             | V           |                   |

| Power consumption             |       | 2.1       |             | W           |                   |

| Junction temperature          | -25   | 50        | 125         | $^{\circ}C$ |                   |

|                               |       | put Data  | ı (data in) |             |                   |

| Data Rate                     | 1     |           | 2000        | Mbps        |                   |

| Swing (SE)                    |       | 1.5       |             | V           | Peak-to-peak      |

| CM Voltage Level              |       | 750       |             | mV          |                   |

| Allowed V <sub>IH</sub> range | 1.1   |           | 1.8         | V           |                   |

| Allowed V <sub>IL</sub> range | 0     |           | 450         | mV          |                   |

|                               |       | iput Clo  | ek (clk in) |             | 1                 |

| Frequency                     | 1     |           | 2000        | MHz         |                   |

| Swing (SE)                    |       | 1.5       |             | V           | Peak-to-peak      |

| CM Voltage Level              |       | 750       |             | mV          |                   |

|                               | _     | tput Data | a (data out | t)          | 1                 |

| Data Rate                     | 0.5   |           | 1000        | Mbps        |                   |

| Swing (SE)                    |       | 1.5       |             | V           | Peak-to-peak      |

| CM Voltage Level              |       | 750       |             | mV          |                   |

| Interface                     |       | SSTL1.5   |             |             |                   |

|                               |       | Output C  | lock (clk o |             | 1                 |

| Frequency                     | 1     |           | 2000        | MHz         |                   |

| Swing (SE)                    |       | 1.5       |             | V           | Peak-to-peak      |

| CM Voltage Level              |       | 750       |             | mV          |                   |

| Interface                     |       | SSTL1.5   |             |             |                   |

|                               |       |           | rameters    |             | 1                 |

| clk_in to clk_out             | 420   | 510       | 560         | ps          |                   |

| clk_in to c2_out              | 640   | 780       | 880         | ps          | Propagation delay |

| clk_in to c4_out              | 640   | 760       | 890         | ps          |                   |

| Data skew                     |       | 0         |             | ps          | Dy simulation     |

| Clock skew                    |       | 0         |             | ps          | By simulation     |

| $	au_{\mathrm{cdi1}}$         | 200   | 245       | 300         | ps          |                   |

| $	au_{ m cdi2}$               | 230   | 275       | 330         | ps          |                   |

| $	au_{ m c2d}$                | 9     | 20        | 24          | ps          |                   |

| $\tau_{c2c4}$                 | 0     | 1         | -1          | ps          |                   |

#### PACKAGE INFORMATION

The chip is packaged in a custom 256-pin BGA package. The drawing of the package is shown in **Fig. 7**.

Fig. 7. BGA Package.

The part's identification label is ASNT2031-MBL. The first 8 characters of the name before the dash identify the bare die including general circuit family, fabrication technology, specific circuit type, and part version while the 3 characters after the dash represent the package's manufacturer, type, and pin out count.

This device complies with the Restriction of Hazardous Substances (RoHS) per 2011/65/EU for all ten substances.

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

# **REVISION HISTORY**

| Revision | Date    | Changes                                |  |

|----------|---------|----------------------------------------|--|

| 1.6.2    | 05-2020 | Updated Package Information            |  |

| 1.5.2    | 07-2019 | Updated Letterhead                     |  |

| 1.5.1    | 01-2013 | Corrected format.                      |  |

|          |         | Added pin out drawing.                 |  |

|          |         | Corrected block diagram.               |  |

|          |         | Added Absolute Maximums Rating table.  |  |

|          |         | Corrected Package Information section. |  |

|          |         | Added Revision History table.          |  |

| 1.4      | 08-2011 | Revised Electrical Characteristics.    |  |

| 1.3      | 08-2011 | Revised Electrical Characteristics.    |  |

| 1.2      | 07-2011 | Revised Electrical Characteristics.    |  |

| 1.1      | 07-2011 | Revised Electrical Characteristics.    |  |

| 1.0      | 06-2011 | First release.                         |  |